이미지 확대보기

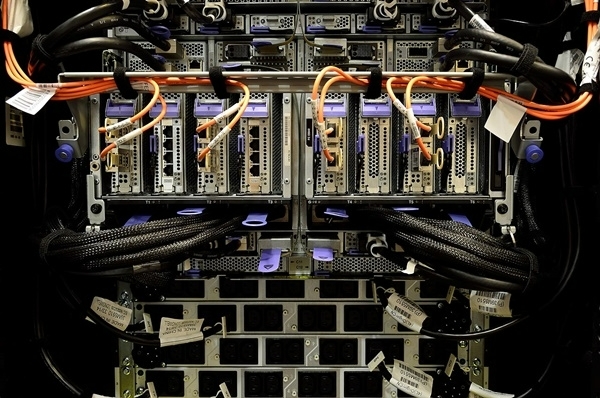

이미지 확대보기삼성전자가 IBM과 함께 ‘수직 적층 트랜지스터’를 개발해 종전의 나노시트 임계값을 깨고 성능이 두 배이거나 전력 사용을 85% 절약 가능한 칩을 개발했다.

미국의 엔가제트와 인터레스팅엔지니어링 등은 12일(현지시간) 삼성전자와 IBM이 샌프란시스코에서 열린 국제전자소자회의(IEDM) 첫날 미국과 중국의 경쟁자들과의 격차를 벌리는 칩을 개발했다고 보도했다.

양 사는 이 회의에서 트랜지스터를 칩에 수직으로 적층하는 새로운 디자인을 공개했다. 전류 프로세서와 SoC를 사용하면 트랜지스터가 실리콘 표면에 평평하게 놓이고 전류가 좌우로 흐른다. 수직 적층 전송 전계 효과 트랜지스터(VTFET)는 전류가 수직으로 흐른다.

이번 칩 개발의 핵심은 1나노미터(nm) 수준 미만의 반도체 제조를 가능하게 하는 반금속 비스무트를 사용하는 공정이었다. 반도체 설계에서 칩의 트랜지스터를 수직으로 적층하는 건 새로운 개념이다. 트랜지스터가 실리콘 표면에 수평으로 놓이고 전류가 좌우로 흐르는 현재 모델을 탈피한 것이다. 이를 통해 IBM과 삼성은 반도체 집적도가 2년마다 2배로 늘어난다는 ‘무어의 법칙’을 나노시트 임계값 이상으로 확장하거나 에너지 낭비를 줄인다고 예측한다.

양 사에 따르면 이 디자인으로 IBM의 현재 나노시트 기술 이상으로 성능이 대폭 향상되거나 혹은 이같은 설계로 더 큰 전류 흐름 덕분에 낭비되는 에너지를 줄인다고 한다. VTFET가 종전 FinFET 트랜지스터로 설계된 칩보다 2배 더 빠르거나 85% 더 적은 전력을 사용하는 프로세서로 이어질 것이라고 추정한다.

이에 따라 이 프로세스가 한 번의 충전으로 일주일 내내 사용할 수 있는 전화기를 만들 수 있다고 주장했다. 또한 크립토마이닝 등 에너지 집약적인 특정 작업을 더 효율적으로 해 환경 피해를 줄인다고 양 사 연구팀은 밝혔다.

삼성전자는 지난해 8월17일 미국 IBM의 차세대 서버용 중앙처리장치(CPU) 파운드리 계약을 수주하면서 이 분야 합작을 발표한 바 있다. IBM은 차세대 서버용 CPU ‘파워(power) 10’을 삼성전자가 생산한다고 밝혔다. 이는 극자외선(EUV) 기반 7나노 공정에 기반한 것으로 알려졌다. 이밖에 삼성전자는 IBM과 10년간 공동 연구개발을 발표했는데 파운드리 분야에서 치열하게 경쟁하는 대만의 TSMC와의 사이에서 이룬 쾌거였다.

남호영 글로벌이코노믹 기자 nhy@g-enews.com

![[모바일 랭킹] 넷마블 신작 '아스달 연대기' 매출 최고 4위 기록](https://nimage.g-enews.com/phpwas/restmb_setimgmake.php?w=155&h=116&m=1&simg=2024050413590602929c5fa75ef8612254575.jpg)